National Aeronautics and Space Administration

www.nasa.gov

## **Burn-in of Microcircuits**

## 2015 Electronics Technology Workshop (ETW) NASA Electronic Parts and Packaging Program (NEPP)

GSFC, Greenbelt, Maryland June 23–26, 2015

S. Agarwal NASA - Jet Propulsion Laboratory, California Institute of Technology Pasadena, California, USA Shri.g.agarwal@jpl.nasa.gov

Copyright 2015. All rights reserved

The Rover Environmental Monitoring Station (REMS) on NASA's Curiosity Mars rover includes temperature and humidity sensors mounted on the rover's mast. One of the REMS booms extends to the left from the mast in this view. Image credit: NASA/JPL-Caltech/MSSS

## Abstract

Burn-in (BI) is the key screening step for electronic components. It is performed to reduce product infant mortality by weeding out parts susceptible to early failure. Our recent audit and specification work has shown that the microcircuits burn-in screening requirements as stated in MIL-STD-883, Test Method 5004, are out of date and can have multiple interpretations. At the request of NASA, the Aerospace Corporation, and other concerned organizations, a JC13 Task Group was formed to provide guidance. This paper will describe the issues and provide a status update on microcircuit burn-ins. This work was performed for NEPAG, the NASA Electronic Parts Assurance Group.

## Microcircuits Burn-in (BI) Screening Requirements Are out of Date and Have Multiple Interpretations

- Bl is the key screening step considered necessary to weed out product infant mortality.

- Our recent audit and specification review work has shown that the microcircuits BI screening requirements as stated in MIL-STD-883, Test Method 5004, are out of date and have multiple interpretations.

- Why are they out of date?

- Were developed more than 25 years ago

- Then: were at 5-micron technology node

- Now: 45-nm space products are on their way to QMLV qualification (Ref: Lew Cohn's talk on Tuesday). Made possible by

- o Dual use technology

- Advances in packaging technology

- Availability of system-on-a-chip (SOC) products, which could be easily called assemblies

- With column grid arrays (CGAs), reached limitation for complete screening.

- Changing business landscape

## Microcircuits Burn-in (BI) Screening Requirements Are out of Date and Have Multiple Interpretations (Cont'd)

- No clear interpretation any longer

- Varied implementation

- Periodic, frequent updates are needed!

- Recent Activities

- At the request of NASA, the Aerospace Corporation and others, a new JC13 Task Group was formed to provide guidance.

- More rigorous assessment done during audits and specification reviews.

## Findings from Microcircuit Audits & New Technology Data Reviews

**Supplier audits.** The audit team reviews screening travelers and burn-in circuits (Done on one or two typical products used on space programs). Some of the findings were:

- Disabled chip burn-ins. Recent audit for QML device discovered that a chip was disabled during static burn-in; thus, it was not drawing any current. *Recommendation:* For new SMDs, add a statement within burn-in paragraphs stating that parts shall be kept in their enabled state during burn-in.

- Class Q 160-hr/125°C burn-in. Interpreted as static burn-in. *Recommendation:* Provide specific guidelines in MIL-STD-883, Test Method 5004.

- At-frequency (dynamic) burn-ins. Test equipment limitation cited for not doing burn-ins at application frequency.

*Recommendation:* Burn-in task group to discuss and provide guidance. When SMD says that a part can be used at 200 MHz, doing burn-in at 6 MHz (cited as "burn-in equipment limitation frequency") is not meaningful!

- Two static burn-ins. Some manufacturers do electrical testing between two static burnins, whereas others do electricals after completing both static burn-ins. *Recommendation:* Provide specific guidelines in MIL-STD-883, Test Method 5004.

- **Thermal imaging.** For a device with hot spots, thermal resistance, junction-to-case would be much higher than guidelines given in MIL-STD-1835. One supplier used thermal imaging to find hot spots on the die.

*Recommendation:* Assign a task group to evaluate effectiveness of thermal imaging at product development stage.

## **NASA Inputs to BI Task Group**

- Clarify burn-in requirements for space products in Table I of Method 5004: specifically, screening steps 3.1.10, 3.1.12, footnote 9/, and footnote 10/. As written, it implies that dynamic burn-in is a requirement. However, this is not always done. Moreover, for certain functions, such as a precision voltage reference, how would you design a dynamic burn-in? Requirements need to be reviewed and updated.

- High-temperature reverse bias (HTRB) vs. static burn-in. Table I of Method 5004 has no mention of static burn-in. We all know that digital products are subjected to static burn-ins, often two: one for low condition (Static I) and the other for high condition (Static II). Add reference to static burn-in(s) as appropriate.

- 3. How are burn-in voltage, frequency, etc. supposed to be determined?

- 4. Are any manufacturers using low temperature burn-in? If yes, a low-temp burn-in option should be included in the screening spec.

- 5. What activation energy (Ea) should be used for new technology? Some manufacturers are using a fixed Ea of 0.7 eV.

- 6. Time-temperature regression tables (e.g., Table I in Method 1015) should be reviewed.

What Ea are they based on? Is that Ea still valid?

## NASA Inputs to BI Task Group (Cont'd)

#### 7. Limited-temperature parts:

- Anything not meeting full MIL temperature range (–55°C to +125°C)

- If the part rating has a maximum temperature less than +125°C, what is the temperature and duration of the burn-in?

#### 8. Dynamic burn-in for high-speed devices.

• What frequency should be used?

## Additional NASA Inputs to JC13 Task Group Static Burn-in Circuits

- Considerable variation on how they are implemented.

- Single circuit used with half of the inputs biased low and the other half biased high.

- o Post static burn-in electricals done.

- Two Circuits used.

- All inputs low (Static I)

- All inputs high (Static II)

- Post static burn-in electricals done after completion of both (Static I and Static II) burn-ins.

- Two circuits used.

- All inputs low (Static I)

- o All inputs high (Static II)

- Post static burn-in electricals done after completion of each static burn-in.

- Task Group review and guidance requested. Also, clarify which inputs are being used and their settings: data, control, address, clock,...?

## Task Group – 2011-01 SMD Electrical and Burn-in Guidelines

- Charter for Task Group. Develop JEDEC document for guidance to suppliers and users that includes recommendations on Deltas, SMD electrical parameters, and Burn-in. Also, provide recommendations for any needed changes to MIL-STD-883.

- 1. Burn-In

- a. types required dynamic and static/high-temperature reverse-bias burn-in (HTRB)

- b. burn-in specified by technology or product type

- c. junction temperatures to be achieved

- d. burn-in conditions voltages, frequency, etc.

#### 2. Delta Requirements

a. definition - critical parameters selected to provide a measure of product and process stability b. selection of delta parameters

#### 3. Electrical Measurements

- a. parametrics

- b. functional

- c. selection of limits based on what?

- d. parameters guaranteed

- 1) but not tested

- 2) by design

- 3) by characterization data

- 4) data required to validate guaranteed position

## **New JEDEC Document**

- In draft form, expected release September 2015

- Title: Selection of burn-in/life test conditions and critical parameters for QML microcircuits

- The document covers

- Terms and definitions

- Burn-in stress and electrical test conditions development

- Burn-in conditions evaluations

- Burn-in and electrical measurements

- Will be a guideline document

- The Task Group will remain open to address the remaining issues

## **Issues Going Forward**

- Alternate methods for deep submicron technologies

- Wafer level burn-in, others

- Limited-temperature (restricted-temperature) range parts

- BI temperature

- BI duration time/temp table in TM 1015, applies to hybrids but is not applicable to monolithic microcircuits

- What temp range to do final (post BI) electricals

- New technology CGAs

- Suppliers don't recommend post-CGA BI

- How to ensure infant mortality removal after installation of columns

- Low leakage currents and their delta limits

- Burn-in of high-speed parts

- Hybrids parts

- BI temperature, time, voltage

- Element evaluation burn-in

- Hybrid crystal oscillators

- BI temperature, time, voltage

- Any other issues as they arise

## **Dual Use Technology**

200

225

250

device(s) does not go into thermal runeway.

3/ The only allowed conditions are as stated above.

- Basically an infusion of commercial ٠ monolithic microcircuits into DoD system

- Rad hard by design 45nm CMOS microelectronics technology (BAE Systems, built at IBM foundry)

- Adding their unique processing ste to the existing processes, e.g. MRAMs being offered by Aeroflex Honeywell (done in collaboration v Everspin)

- Upscreening selected products fro commercial portfolio (Analog Devic

- This has resulted in paradigm changes. ٠ example follows:

- Not all parts are specified over the military temperature range, -55°C to +125°C. Many of them are specified over -40°C to +110°C operating temperature range. These differences are now clearly shown in the standard microcircuit drawings (SMDs). However, there are **no** guidelines for BI of these devices. (Per notes 3/ and 4/ of the regression table, doing BI at temperatures lower than 125°C is not allowed for monolithic microcircuits.)

| 1.          |                                    |               |                |                                    |                        |                           |

|-------------|------------------------------------|---------------|----------------|------------------------------------|------------------------|---------------------------|

|             | Minimum                            |               | Minimum time ( | hours)                             | Test                   | Minimum                   |

|             | temperature<br>T <sub>A</sub> (*C) | Class level S | Class level B  | Class level S hybrids<br>(Class K) | condition<br>(see 3.1) | reburn-in<br>time (hours) |

|             | 100                                | -             | 352            | 700                                | Hybrids only           | 24                        |

| eps         | 105                                | -             | 300            | 600                                | •                      | 24                        |

| a la d      | 110                                | _             | 260            | 520                                | -                      | 24                        |

| and<br>with | 115                                | _             | 220            | 440                                | •                      | 24                        |

| VVI (III    | 120                                | _             | 190            | 380                                | •                      | 24                        |

| om          | 125                                | 240           | 160            | 320                                | A-E                    | 24                        |

| ces)        | 130                                | 208           | 138            | -                                  | •                      | 21                        |

|             | 135                                | 190           | 120            | _                                  | •                      | 18                        |

| An          | 140                                | 160           | 105            | -                                  | •                      | 16                        |

| / 11        | 145                                | 140           | 92             | -                                  | •                      | 14                        |

| e full      | 150                                | 120           | 80             | -                                  | •                      | 12                        |

| to          | 175                                | _             | 48             | _                                  | F                      | 12                        |

28

16

12

4/ Test temperatures below 125°C may be used for hybrid circuits only.

1/ Test condition F shall be authorized prior to use and consists of temperatures 175°C and higher.

For condition F the maximum junction temperature is unlimited and care shall be taken to ensure the

\_

•

.

.

#### MIL-STD-663J WCHANGE 1

TABLE I. Burn-In time-temperature regression. 1/ 2/ 3/ 4/

METHOD 1015.10 26 February 2010

12

12

12

## **Signal Integrity Capacitors**

- Signal integrity capacitors used in microcircuits

- MIL-PRF-38535, Para 3.15.1 specifies screening requirements.

- Base metal electrode (BME) capacitors used with low-voltage high speed microcircuits do not meet Para 3.15.1.

- BMEs were meant to be used in commercial applications.

- However, the upscreened versions of the BMEs have also found their way into microcircuits and hybrids of interest to the space community.

- The suitability of BMEs for use in space applications is being evaluated by

- ➢ JEDEC, G12, NASA, Aerospace, ESA, and JAXA.

- The goal is to have an acceptable screening flow this fiscal year. (MIL-PRF-THIN and associated slash sheets)

- It should be noted that these screened BME capacitors would see additional screening including the burn-in(s) at the unit level.

## **Other Updates on Microcircuits**

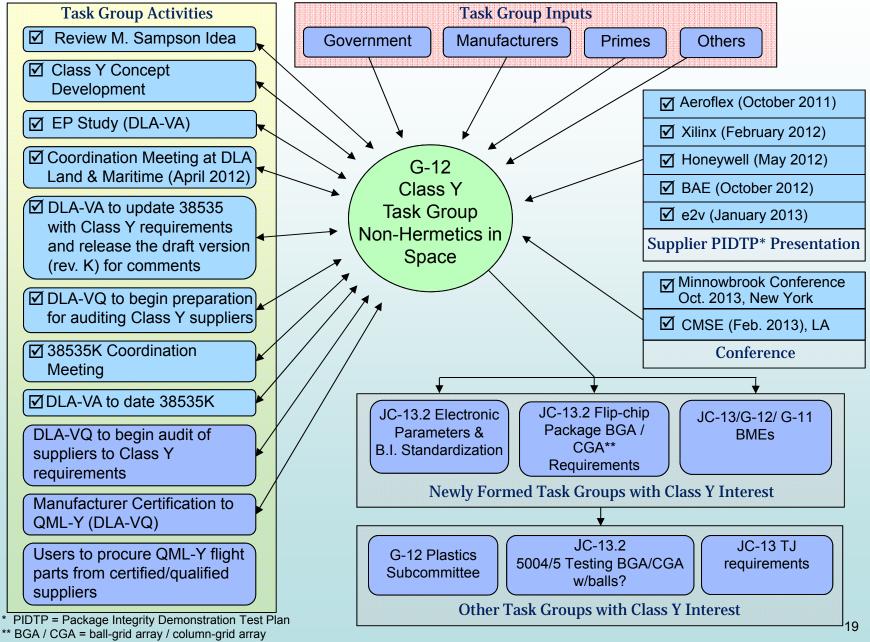

#### Class Y

- A new class created for complex ceramic based non-hermetic microcircuits

- Introduced PIDTP (Package Integrity Demonstration Test Plan)

- MIL-PRF-38535K (the latest revision) includes requirements for Class Y.

- Front-runner suppliers: Xilinx, Honeywell, Cobham/Aeroflex, e2v

- Currently addressing testing of underfill and thermal interface material (TIM) adhesive to meet the requirements of MIL-STD-883, Test Method 5011.

- Manufacturers have the requirements; we will see what works and what needs changing in actual practice.

- Signal Integrity Capacitors

- Slash sheets for InterDigitated Capacitors (IDCs) used in Xilinx V-5 FPGAs are yet to be developed.

- PEMs Upscreening Flows

- Flows developed for terrestrial and space applications

- Bond wires used in plastic encapsulated microcircuits (PEMs)

- New industry effort started for copper bond wires weekly telecons

- JC13.7 Task Group

- New electronic device technology trends

- Trying to get standards in front of technology.

- Refer to JEDEC/G12 websites for details

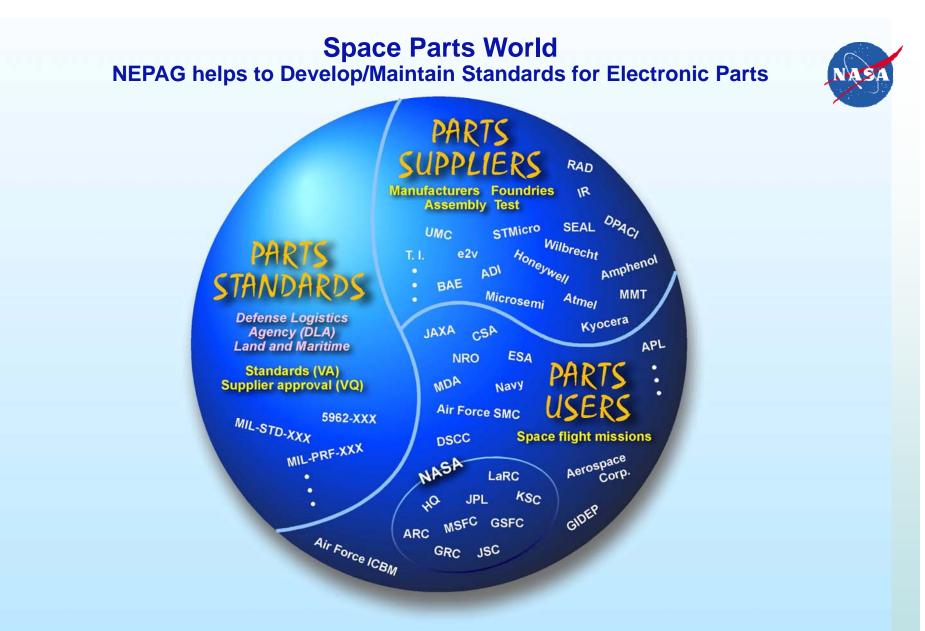

The parts users and standards organizations work with suppliers to ensure availability of standard parts for NASA, DoD and others. For Space microcircuits, DLA, NASA (S. Agarwal) and the U.S. Air Force / Aerospace Corp. (L. Harzstark) form the Qualifying Activity (QA).

## MIL-STD-883, Test Method 1005

#### MIL-STD-883J w/CHANGE 1

| Minimum<br>temperature<br>T <sub>A</sub> (°C ) |                  | Test<br>condition<br>(see 3.5) |                                       |             |

|------------------------------------------------|------------------|--------------------------------|---------------------------------------|-------------|

|                                                | Class level<br>S | Class level<br>B               | Class level S<br>hybrids<br>(Class K) |             |

| 100                                            |                  | 7500                           | 7500                                  | Hybrid only |

| 105                                            |                  | 4500                           | 4500                                  |             |

| 110                                            |                  | 3000                           | 3000                                  |             |

| 115                                            |                  | 2000                           | 2000                                  |             |

| 120                                            |                  | 1500                           | 1500                                  |             |

| 125                                            | 1000             | 1000                           | 1000                                  | A-E         |

| 130                                            | 900              | 704                            | _                                     |             |

| 135                                            | 800              | 496                            | _                                     |             |

| 140                                            | 700              | 352                            | _                                     |             |

| 145                                            | <del>6</del> 00  | 256                            | _                                     |             |

| 150                                            | 500              | 184                            | _                                     | •           |

| 175                                            |                  | 40                             | _                                     | F           |

| 180                                            |                  | 32                             | _                                     | u           |

| 185                                            |                  | 31                             | _                                     | н           |

| 190                                            |                  | 30                             | _                                     | u           |

#### TABLE I. Steady-state time temperature regression. 1/2/3/4/

Test condition F shall be authorized prior to use and consists of temperatures 175°C V and higher.

For condition F the maximum junction temperature is unlimited and care shall be taken 2 to ensure the device(s) does not go into thermal runaway.

3/ 4/ The only allowed conditions are as stated above.

Test temperatures below 125°C may be used for hybrid circuits only.

**METHOD 1005.9** 26 February 2010

Life test below 125C not allowed for monolithic microcircuits. •

## MIL-PRF-38535, Revision K

#### MIL-PRF-38535K

TABLE IA. Screening procedure for hermetic classes Q. V and non-hermetic class Y microdircuits.

| Qt Tt-                                                                               | MIL-STD-883, test method (TM) and conditions              |                                                                                    |                                                                                   |  |  |

|--------------------------------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|--|

| Screening Tests                                                                      | Class Q<br>(class level B)                                | Class V<br>(class level S)                                                         | Class Y<br>(class level S)                                                        |  |  |

| 1. Water lot acceptance test                                                         | QM plan<br>(see H.3.2.1.4) 1/                             | QM plan (see H.3.2.1.4) <u>1</u> /<br>or<br>TM 5007 of MIL-STD-883<br>(all lots)   | QM plan (see H.3.2.1.4) 1/<br>or<br>TM 5007 of ML-STD-663<br>(all lots)           |  |  |

| 2. Nondestructive bond pull (NDBP) test 2/                                           |                                                           | TM 2023                                                                            | TM 2023                                                                           |  |  |

| 3. Internal viewal inspection 3/                                                     | TM 2010, condition B                                      | TM 2010, condition A                                                               | TM 2010, condition A                                                              |  |  |

| 4. Temperature cycling 4/                                                            | TM 1010, condition C,<br>10 cycles minimum                | TM 1010, condition C,<br>10 cycles minimum                                         | TM 1010, condition C,<br>10 cycles minimum                                        |  |  |

| 5. Constant acceleration 5/                                                          | TM 2001, condition E<br>(minimum), Y1 orientation<br>only | TM 2001, condition E<br>(minimum), Y1 orientation<br>only                          | TM 2001, condition E<br>(minimum), Y1 orientation<br>only                         |  |  |

| 6. Visual inspection <u>6</u> /                                                      | 100%                                                      | 100%                                                                               | 100%                                                                              |  |  |

| 7. Particle Impact Noise Detection<br>(PIND) test 7/ 3/                              |                                                           | TM 2020, test condition A<br>on each device                                        | TM 2020, test condition A<br>on each device                                       |  |  |

| 8. Serialization <u>9</u> /                                                          | In accordance with device<br>specification (100%)         | In accordance with device<br>specification (100%)                                  | In accordance with device<br>specification (100%)                                 |  |  |

| 9. Pre burn-in (Interim) electrical<br>perameters test <u>10</u> /                   | In accordance with device specification <u>11</u> /       | In accordance with device specification <u>12</u> /                                | In accordance with device specification <u>12</u> /                               |  |  |

| 10. Burn-In test:<br><u>10</u> / <u>13/</u> <u>14/</u>                               | TM 1015<br>160 hours at +125°C<br>minimum                 | TM 1015<br>240 hours at 125°C,<br>condition D <u>15</u> /                          | TM 1015<br>240 hours at 125°C ,<br>condition D <u>15</u> /                        |  |  |

| <ol> <li>Post burn-in (interim) electrical<br/>parameters test <u>10</u>/</li> </ol> |                                                           | In accordance with device specification <u>12</u> /                                | In accordance with device specification <u>12</u> /                               |  |  |

| 12. Revense blas burn-in test<br>(Static burn-in)<br>13/14/16/                       |                                                           | TM 1015, Condition A or C;<br>144 hours at +125°C or<br>72 hours at +150°C minimum | TM 1015, Condition A or C;<br>144 hours at +125°C or<br>72 hours at +150°C minimu |  |  |

| 13. Post bum-in (interim-reverse bias)<br>electrical parameters test <u>10</u> /     |                                                           | In accordance with device specification <u>12</u> /                                | In accordance with device specification <u>12</u> /                               |  |  |

• Step 12 now includes option for static burn-in

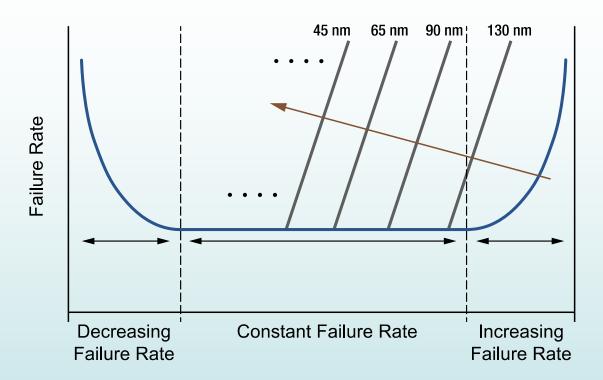

## **Bathtub Curve and Feature Sizes**

It has been reported that as the feature sizes get smaller, the product useful life gets shorter. This should be further investigated if considering use of COTS with small features, particularly below 45nm (e.g., 35nm, 28nm, 20nm, 14nm).

## Infusion of New Technology into the QML System G12 Class Y Effort at a Glance (e.g. Xilinx V4/V5 FPGAs)

## http://nepp.nasa.gov

# NEPAG

#### ACKNOWLEDGMENTS

The research described in this publication was carried out, in part, at the Jet Propulsion Laboratory, California Institute of Technology, under a contract with the National Aeronautics and Space Administration. Help is gratefully acknowledged from J. Park, R. Carlson, R. Menke, D. Sheldon, and M. Sampson. Copyright 2015 California Institute of Technology. Government sponsorship acknowledged.